# Verilog Digital System Design

SECOND EDITION

- ✓ Verilog 2001

- ✓ Test-bench development

- ✓ OVL Verification Library

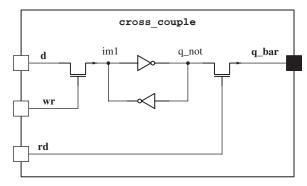

- ✓ New synthesis standards

Zainalabedin Navabi

## Verilog Digital System Design

RT Level Synthesis, Testbench and Verification

#### Zainalabedin Navabi, Ph.D.

Professor of Electrical and Computer Engineering Northeastern University Boston, Massachusetts

Second Edition

McGraw-Hill

Copyright © 2006 by The McGraw-Hill Publishing Companies, Inc. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

0-07-158892-2

The material in this eBook also appears in the print version of this title: 0-07-144564-1.

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at george\_hoare@mcgraw-hill.com or (212) 904-4069.

#### TERMS OF USE

This is a copyrighted work and The McGraw-Hill Companies, Inc. ("McGraw-Hill") and its licensors reserve all rights in and to the work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill's prior consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your right to use the work may be terminated if you fail

to comply with these terms.

THE WORK IS PROVIDED "AS IS." McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WARRANTIES AS TO THE ACCURACY, ADEQUACY OR COMPLETE-NESS OF OR RESULTS TO BE OBTAINED FROM USING THE WORK, INCLUDING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. McGraw-Hill and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071445641

## Want to learn more?

We hope you enjoy this McGraw-Hill eBook! If

you'd like more information about this book, its author, or related books and websites, please click here.

To my mother, Sadri Kheradmand (Navabi), who inspired me to pursue a life of science and engineering.

## **Contents**

#### Preface xiii

| Chapt | er 1. Di                         | igital System Design Automation with Verilog | 1  |

|-------|----------------------------------|----------------------------------------------|----|

| 1.1   | Digital                          | Design Flow                                  | 2  |

|       | 1.1.1                            | Design entry                                 | 3  |

|       | 1.1.2                            | Testbench in Verilog                         | 4  |

|       | 1.1.3                            | Design validation                            | 4  |

|       | 1.1.4                            | Compilation and synthesis                    | 7  |

|       |                                  | Postsynthesis simulation                     | 10 |

|       |                                  | Timing analysis                              | 10 |

|       | 1.1.7                            | Hardware generation                          | 10 |

| 1.2   | Verilog                          | HDL                                          | 10 |

|       | 1.2.1                            | Verilog evolution                            | 11 |

|       | 1.2.2                            | Verilog attributes                           | 11 |

|       | 1.2.3                            | The Verilog language                         | 13 |

| 1.3   | Summary                          |                                              | 13 |

|       | Problems                         |                                              | 13 |

|       | Sugge                            | sted Reading                                 | 14 |

| Chapt | er 2. Ro                         | egister Transfer Level Design with Verilog   | 15 |

| 2.1   | RT Level Design                  |                                              | 15 |

|       | 2.1.1                            | Control/data partitioning                    | 16 |

|       | 2.1.2                            | Data part                                    | 16 |

|       | 2.1.3                            | Control part                                 | 17 |

| 2.2   | Elemei                           | nts of Verilog                               | 18 |

|       | 2.2.1                            | Hardware modules                             | 18 |

|       | 2.2.2                            | Primitive instantiations                     | 19 |

|       | 2.2.3                            | Assign statements                            | 20 |

|       | 2.2.4                            | Condition expression                         | 20 |

|       | 2.2.5                            | Procedural blocks                            | 20 |

|       | 2.2.6                            | Module instantiations                        | 21 |

| 2.3   | Component Description in Verilog |                                              |    |

#### vi Contents

|                                         | 2.3.1    | Data components                             | 22       |

|-----------------------------------------|----------|---------------------------------------------|----------|

|                                         | 2.3.2    | Controllers                                 | 29       |

| 2.4                                     | Testbe   | nches                                       | 33       |

|                                         |          | A simple tester                             | 33       |

|                                         | 2.4.2    | Tasks and functions                         | 34       |

| 2.5                                     | Summa    | ary                                         | 34       |

|                                         | Proble   | ms                                          | 35       |

|                                         | Sugges   | sted Reading                                | 35       |

| Chapte                                  | er 3. Ve | erilog Language Concepts                    | 37       |

| 3.1                                     |          | eterizing Hardware Languages                | 37       |

| • • • • • • • • • • • • • • • • • • • • | 3.1.1    | Timing                                      | 37       |

|                                         | 3.1.2    | 3                                           | 39       |

|                                         | -        | Timing and concurrency example              | 40       |

| 3.2                                     |          | e Basics                                    | 41       |

|                                         |          | Code format                                 | 41       |

|                                         |          | Logic value system                          | 41       |

|                                         |          | Wires and variables                         | 42       |

|                                         | 3.2.4    | Modules                                     | 42       |

|                                         | 3.2.5    | Module ports                                | 43       |

|                                         | 3.2.6    | Names                                       | 43       |

|                                         | 3.2.7    | Numbers                                     | 44       |

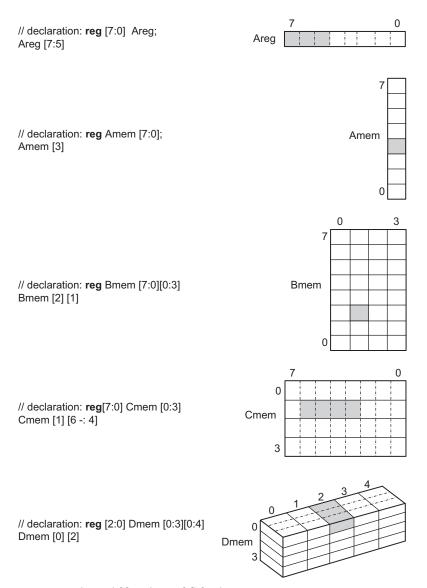

|                                         |          | Arrays                                      | 46       |

|                                         |          | Verilog operators                           | 48       |

|                                         |          | Verilog data types                          | 54       |

|                                         |          | Array indexing                              | 58       |

| 3.3                                     | _        | Simulation Model                            | 59       |

|                                         | 3.3.1    | <b>3</b>                                    | 61       |

|                                         |          | Procedural assignments                      | 65       |

| 3.4                                     |          | ler Directives                              | 71       |

|                                         |          | `timescale                                  | 71       |

|                                         |          | `default-nettype                            | 71       |

|                                         |          | include                                     | 71       |

|                                         | -        | `define                                     | 71<br>72 |

|                                         |          | `ifdef, `else, `endif<br>`unconnected-drive | 72<br>72 |

|                                         |          | `celldefine, `endcelldefine                 | 72       |

|                                         |          | resetall                                    | 72       |

| 3.5                                     |          | Tasks and Functions                         | 72       |

|                                         | 3.5.1    | Display tasks                               | 73       |

|                                         |          | File I/O tasks                              | 73       |

|                                         | 3.5.3    | Timescale tasks                             | 74       |

|                                         | 3.5.4    | Simulation control tasks                    | 74       |

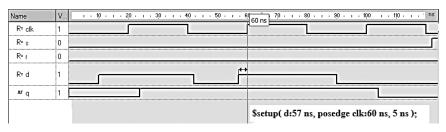

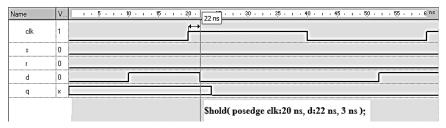

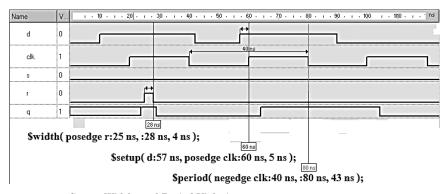

|                                         |          | Timing check tasks                          | 74       |

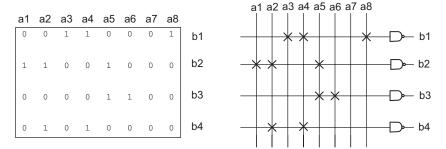

|                                         |          | PLA modeling tasks                          | 74       |

|                                         |          | Conversion functions for reals              | 75       |

|                                         | 3.5.8    | Other tasks and functions                   | 75       |

| 3.6                                     | Summa    | ary                                         | 76       |

|                                         | Problems |                                             | 76       |

|                                         | Sugges   | sted Reading                                | 80       |

|        |          |                                                | Contents | vii        |

|--------|----------|------------------------------------------------|----------|------------|

| Chapte | er 4. Co | ombinational Circuit Description               |          | 81         |

| 4.1    | Module   | e Wires                                        |          | 81         |

|        | 4.1.1    | Ports                                          |          | 81         |

|        | 4.1.2    | Interconnections                               |          | 82         |

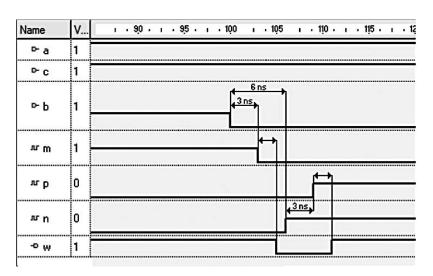

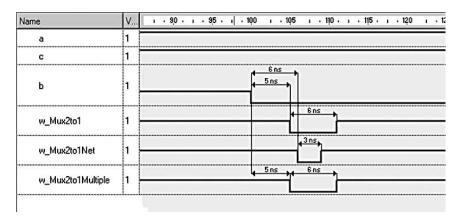

|        | 4.1.3    | Wire values and timing                         |          | 82         |

|        | 4.1.4    | A simple testbench                             |          | 84         |

| 4.2    | Gate L   | evel Logic                                     |          | 85         |

|        | 4.2.1    | Gate primitives                                |          | 85         |

|        | 4.2.2    | User defined primitives                        |          | 87         |

|        | 4.2.3    | Delay formats                                  |          | 88         |

|        | 4.2.4    | Module parameters                              |          | 90         |

| 4.3    | Hierard  | chical Structures                              |          | 93         |

|        | 4.3.1    | Simple hierarchies                             |          | 93         |

|        | 4.3.2    | Vector declarations                            |          | 95         |

|        | 4.3.3    | Iterative structures                           |          | 96         |

|        | 4.3.4    | Module path delay                              |          | 99         |

| 4.4    | Descri   | bing Expressions with Assign Statements        |          | 102        |

|        | 4.4.1    | Bitwise operators                              |          | 102        |

|        | 4.4.2    | Concatenation operators                        |          | 104        |

|        |          | Vector operations                              |          | 104        |

|        |          | Conditional operation                          |          | 105        |

|        |          | Arithmetic expressions in assignments          |          | 108        |

|        |          | Functions in expressions                       |          | 109        |

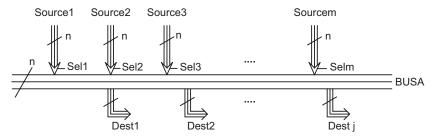

|        |          | Bus structures                                 |          | 110        |

|        |          | Net declaration assignment                     |          | 111        |

| 4.5    |          | oral Combinational Descriptions                |          | 112        |

|        |          | Simple procedural blocks                       |          | 113        |

|        |          | Timing control                                 |          | 113        |

|        |          | Intra-assignment delay                         |          | 116        |

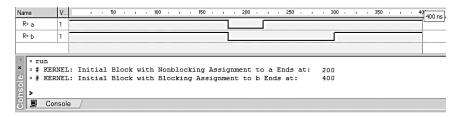

|        |          | Blocking and nonblocking assignments           |          | 116        |

|        |          | Procedural if-else                             |          | 118        |

|        |          | Procedural case statement                      |          | 120        |

|        |          | Procedural for statement                       |          | 122        |

|        |          | Procedural while loop A multilevel description |          | 123<br>124 |

| 4.0    |          | •                                              |          |            |

| 4.6    |          | national Synthesis                             |          | 125        |

|        |          | Gate level synthesis                           |          | 127        |

|       | 4.5.9                   | A multilevel description            | 124 |

|-------|-------------------------|-------------------------------------|-----|

| 4.6   | Combinational Synthesis |                                     | 125 |

|       | 4.6.1                   | Gate level synthesis                | 127 |

|       | 4.6.2                   | Synthesizing continuous assignments | 128 |

|       | 4.6.3                   | Behavioral synthesis                | 129 |

|       | 4.6.4                   | Mixed synthesis                     | 132 |

| 4.7   | Summary                 |                                     | 132 |

|       | Proble                  | ms                                  | 132 |

|       | Sugge                   | sted Reading                        | 134 |

| Chapt | er 5. Se                | equential Circuit Description       | 135 |

| 5.1   | Sequential Models       |                                     | 135 |

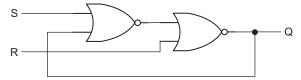

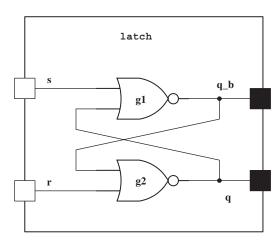

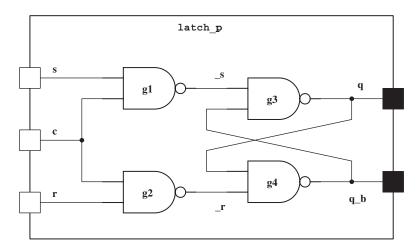

|       | 5.1.1                   | Feedback model                      | 136 |

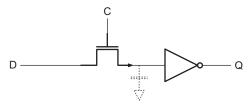

|       | 5.1.2                   | Capacitive model                    | 136 |

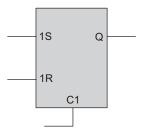

|       | 5.1.3                   | Implicit model                      | 136 |

|       |                         |                                     |     |

#### viii Contents

| 5.2                                     | Basic I  | Memory Components                    | 137        |

|-----------------------------------------|----------|--------------------------------------|------------|

|                                         | 5.2.1    | Gate level primitives                | 137        |

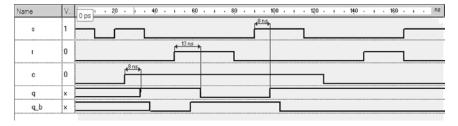

|                                         |          | User defined sequential primitives   | 139        |

|                                         |          | Memory elements using assignments    | 140        |

|                                         |          | Behavioral memory elements           | 142        |

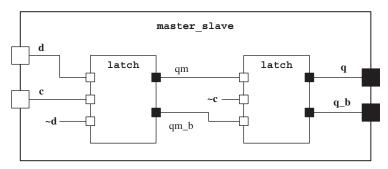

|                                         |          | Flip-Flop timing                     | 149        |

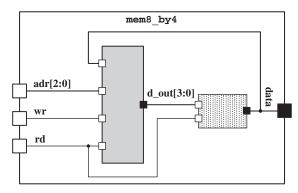

| <b>5</b> 0                              |          | Memory vectors and arrays            | 151        |

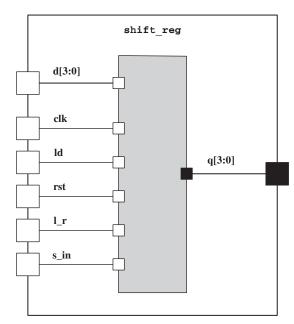

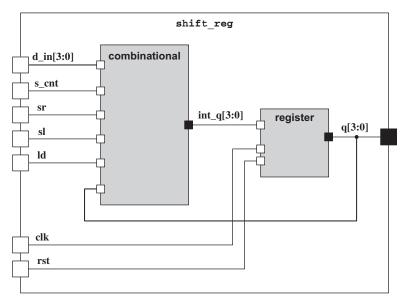

| 5.3                                     | 5.3.1    | onal Registers                       | 157<br>157 |

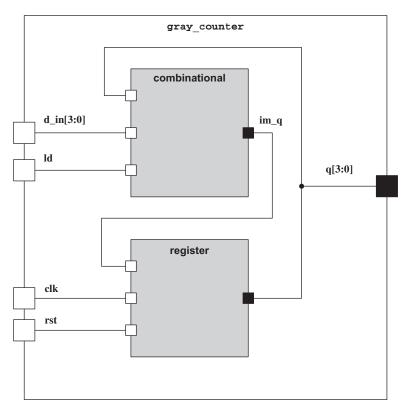

|                                         |          | Shift registers Counters             | 161        |

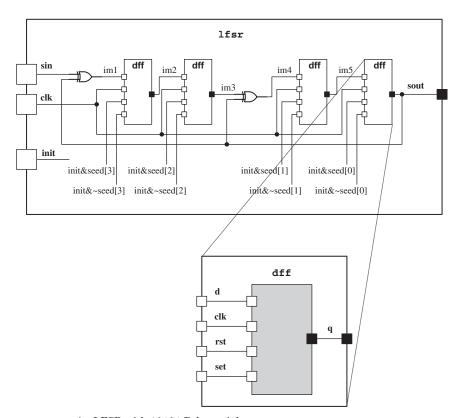

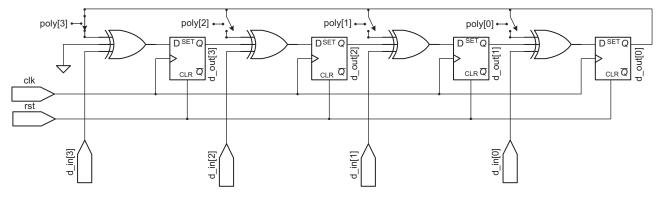

|                                         |          | LFSR and MISR                        | 163        |

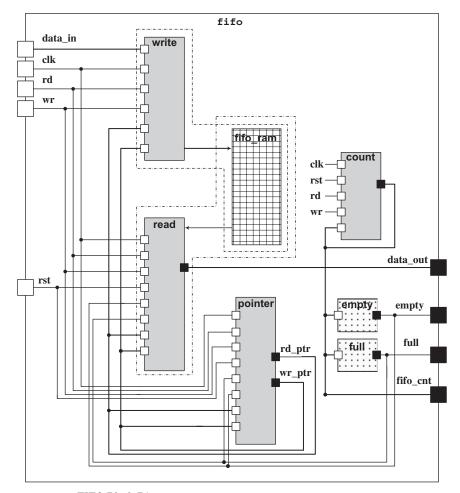

|                                         |          | Stacks and queues                    | 167        |

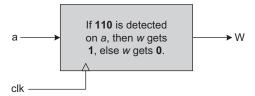

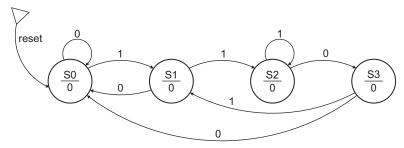

| 5.4                                     |          | Machine Coding                       | 171        |

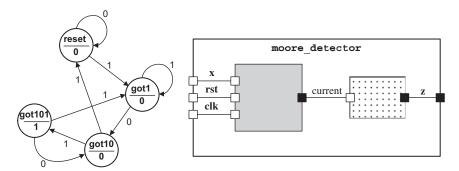

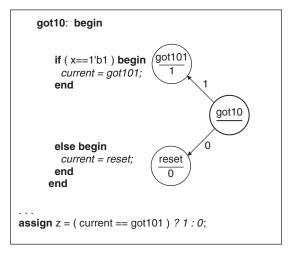

| • • • • • • • • • • • • • • • • • • • • |          | Moore machines                       | 171        |

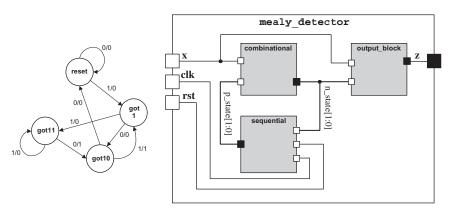

|                                         |          | Mealy machines                       | 174        |

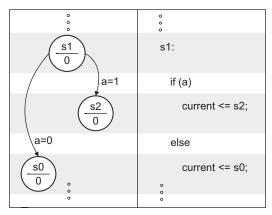

|                                         |          | Huffman coding style                 | 176        |

|                                         |          | A more modular style                 | 180        |

|                                         | 5.4.5    | A ROM based controller               | 181        |

| 5.5                                     | Seque    | ntial Synthesis                      | 181        |

|                                         | 5.5.1    | Latch models                         | 183        |

|                                         | 5.5.2    | Flip-flop models                     | 184        |

|                                         | 5.5.3    | Memory initialization                | 185        |

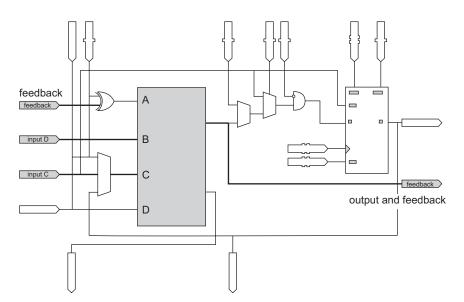

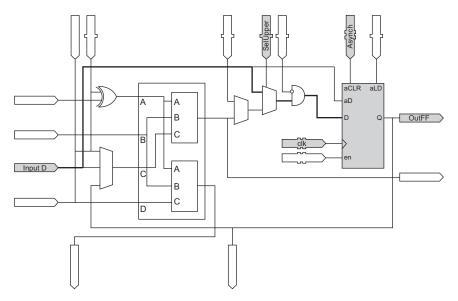

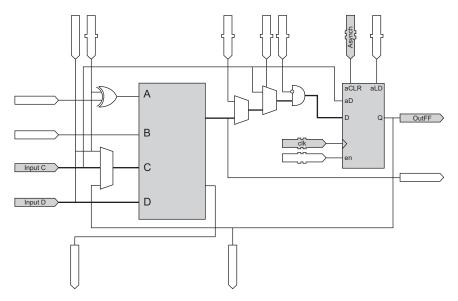

|                                         | 5.5.4    | General sequential circuit synthesis | 186        |

| 5.6                                     | Summa    | ary                                  | 186        |

|                                         | Proble   | ms                                   | 187        |

|                                         | Sugge    | sted Reading                         | 189        |

|                                         |          |                                      |            |

| Chapt                                   | er 6. Co | omponent Test and Verification       | 191        |

| 6.1                                     | Testbe   | nch                                  | 191        |

|                                         | 6.1.1    | Combinational circuit testing        | 192        |

|                                         |          | Sequential circuit testing           | 194        |

| 6.2                                     | Testbe   | nch Techniques                       | 195        |

|                                         | 6.2.1    | Test data                            | 196        |

|                                         | 6.2.2    | Simulation control                   | 197        |

|                                         |          | Limiting data sets                   | 198        |

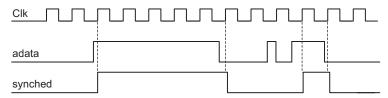

|                                         |          | Applying synchronized data           | 199        |

|                                         |          | Synchronized display of results      | 200        |

|                                         |          | An interactive testbench             | 201        |

|                                         |          | Random time intervals                | 204        |

|                                         |          | Buffered data application            | 205        |

|                                         | •        | Verification                         | 206        |

| 6.4                                     |          | ion Verification                     | 207        |

|                                         |          | Assertion verification benefits      | 208        |

|                                         |          | Open verification library            | 208        |

|                                         |          | Using assertion monitors             | 209        |

| 6 5                                     |          | Assertion templates                  | 216<br>219 |

| 6.5                                     |          | ased Testbenches                     |            |

| 6.6                                     | Summa    | •                                    | 220<br>220 |

|                                         | Problems |                                      |            |

|                                         | Sugge    | sted Reading                         | 221        |

| Contents | ix |

|----------|----|

|          |    |

| Chapte | er 7. De | etailed Modeling                                  | 223        |

|--------|----------|---------------------------------------------------|------------|

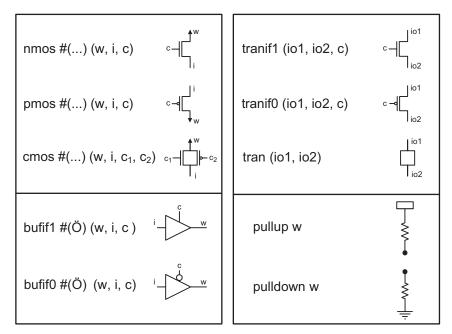

| 7.1    | Switch   | Level Modeling                                    | 223        |

|        | 7.1.1    | Switch level primitives                           | 224        |

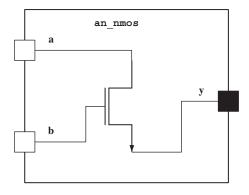

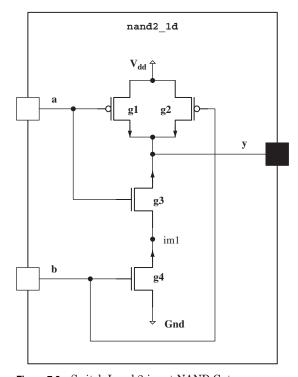

|        |          | The basic switch                                  | 225        |

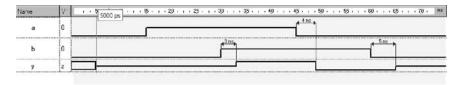

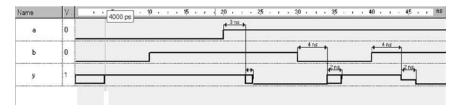

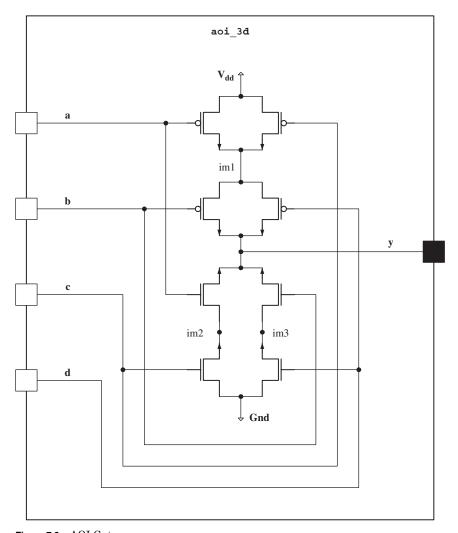

|        |          | CMOS gates                                        | 226        |

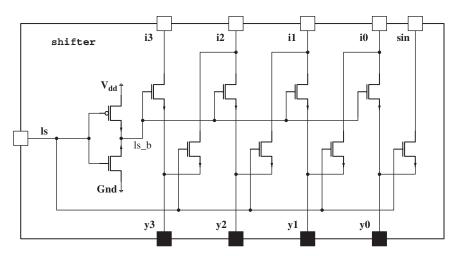

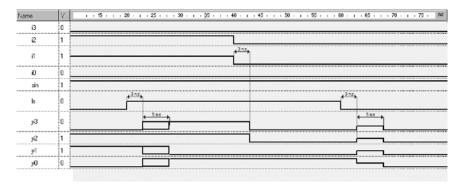

|        |          | Pass gate logic                                   | 230        |

|        |          | Switch level memory elements                      | 234        |

| 7.2    | •        | th Modeling                                       | 241        |

|        |          | Strength values                                   | 242        |

|        |          | Strength used in resolution                       | 244        |

| 7.0    |          | Strength reduction                                | 247        |

| 7.3    | Summa    |                                                   | 250        |

|        | Proble   | <del>-</del>                                      | 250        |

|        | Sugge    | sted Reading                                      | 251        |

| Chapte | er 8. R  | Γ Level Design and Test                           | 253        |

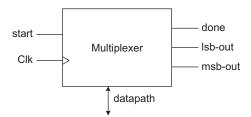

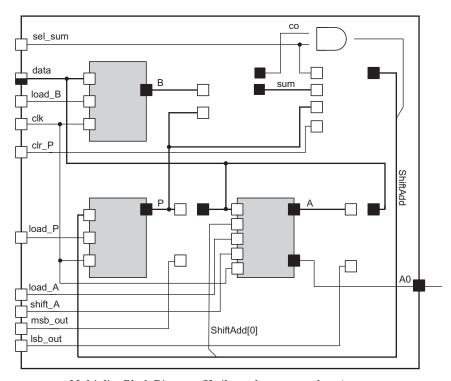

| 8.1    | Sequer   | ntial Multiplier                                  | 253        |

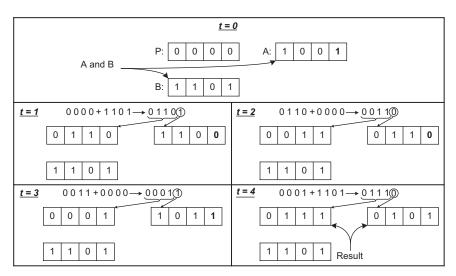

|        | 8.1.1    | Shift-and-add multiplication process              | 254        |

|        | 8.1.2    | Sequential multiplier design                      | 256        |

|        | 8.1.3    | Multiplier testing                                | 261        |

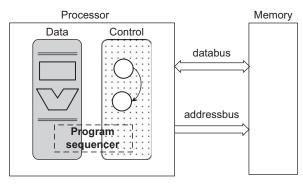

| 8.2    | von Ne   | umann Computer Model                              | 265        |

|        | 8.2.1    | Processor and memory model                        | 265        |

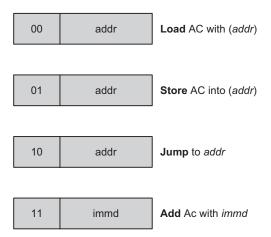

|        |          | Processor model specification                     | 266        |

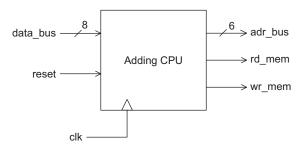

|        |          | Designing the adding CPU                          | 267        |

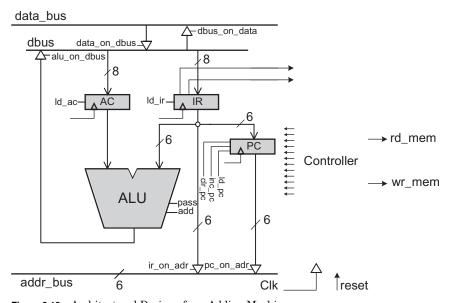

|        |          | Design of datapath                                | 268        |

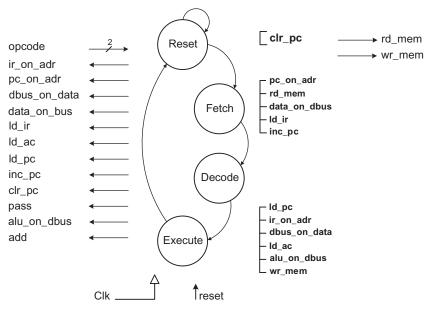

|        |          | Control part design                               | 269<br>270 |

|        |          | Adding CPU Verilog description Testing adding CPU | 270<br>275 |

| 8.3    |          | esign and Test                                    | 281        |

| 0.3    |          | 3                                                 | 281        |

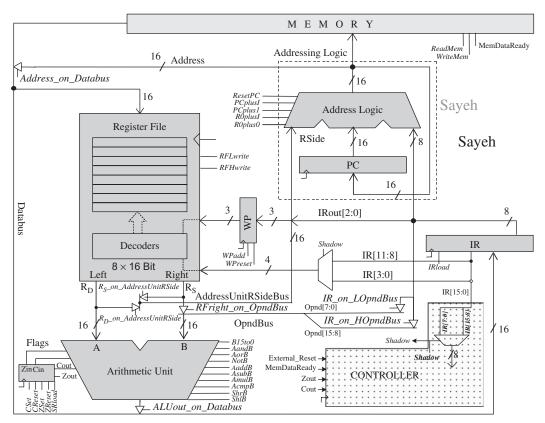

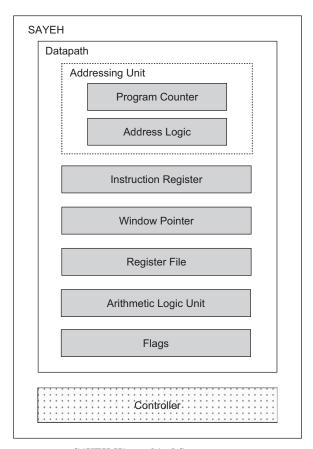

|        |          | Details of processor functionality SAYEH datapath | 283        |

|        |          | SAYEH Verilog description                         | 287        |

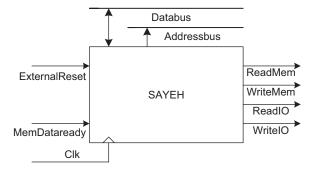

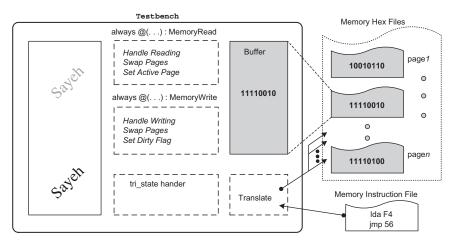

|        |          | SAYEH top-level testbench                         | 298        |

|        |          | Sorting test program                              | 304        |

|        | 8.3.6    | SAYEH hardware realization                        | 304        |

| 8.4    | Summa    | ary                                               | 306        |

|        | Proble   | ms                                                | 306        |

|        | Sugge    | sted Reading                                      | 307        |

| Appen  | dix A.   | List of Keywords                                  | 309        |

| Appen  | dix B.   | Frequently Used System Tasks and Functions        | 311        |

|        |          | Compiler Directives                               | 319        |

|        |          |                                                   |            |

| Appen  | aix D.   | Verilog Formal Syntax Definition                  | 321        |

| Appen  | dix E.   | Verilog Assertion Monitors                        | 345        |

### **Preface**

This book is on the IEEE Standard Hardware Description Language based on the Verilog® Hardware Description Language (Verilog HDL), IEEE Std 1364–2001. The intended audiences are engineers involved in various aspects of digital systems design and manufacturing and students with the basic knowledge of digital system design. The emphasis of the book is on using Verilog HDL for the design, verification, and synthesis of digital systems. We will discuss Register Transfer (RT) level digital system design, and discuss how Verilog can be used in this design flow.

In the last few years RT level design of digital systems has gone through significant changes. Beyond simulation and synthesis that are now part of any RTL design process, we are looking at testbench generation and automatic verification tools. As with any book on Verilog, this book covers digital design and Verilog for simulation and synthesis. However, to ready design engineers for designing, testing, and verifying large digital system designs, the book contains material for testbench development and verification. The subjects of testbench and verification are introduced in Chapter 1. Chapter 2 onwards we concentrate on Verilog for design and synthesis. This will teach the readers efficient Verilog coding techniques for describing actual hardware components. When all of Verilog from a design point of view is presented, we turn our attention to test and verification. Chapter 6 covers testbench development techniques and use of assertion verification monitors for better analysis of a design. Toward the end of the book we put together our coding techniques for synthesis and testbench development, and present several RT level designs from design specification to verification.

Embedded in the presentation of the language, the book provides a review of digital system design and computer architecture concepts. This review is useful for relearning these concepts as demanded by new design methodologies and hardware description language based design tools. For practicing engineers the flow of the book, which starts from

introductory material and advances into complex digital design concepts, provides a self-sufficient learning tool. The material is suitable for an upper division undergraduate or a first year graduate course. For a one-semester course on the Verilog HDL language and its use in a digital system design environment, the book can be used in its entirety. The book can also be used as a supplement for graduate and undergraduate digital system design and computer organization courses.

#### Overview of the Chapters

Chapter overviews are presented below. This material is intended to help a reader concentrate on parts of the book that he or she finds suit able to his or her needs best. Chapters 1 and 2 are introductory, and contain material with which many readers may already be familiar. It is, however, recommended that these chapters not be completely omitted, even by experienced readers. The Verilog language is presented in Chapter 3 and includes the details of language syntax and semantics. The next two chapters (4 and 5) concentrate on Verilog for describing hardware from a design point of view. This is followed by a chapter on testing. Together, Chapters 4, 5, and 6 cover use of Verilog for design and test of digital systems. Chapter 7, which is on detailed modeling, is useful for VLSI designers. The last example in Chapter 8 is a complete processor that is modeled for synthesis and a complete testbench is developed for it.

Chapter 1 gives an overview of digital design process and the use of hardware description languages in this process. Simulation, synthesis, formal verification, and assertion verification are discussed in this chapter.

Chapter 2 shows various ways hardware components can be described in Verilog. The purpose of this chapter is to give the reader a general overview of the Verilog language.

Chapter 3 discusses the complete Verilog language structure. The focus of the chapter is more on the linguistic issues and not on modeling hardware components. A general understanding of the language is necessary before it can be used for hardware modeling. Writing Verilog for describing hardware is discussed in the chapters that follow this chapter.

Chapter 4 starts with gates and ends with high-level Verilog constructs for description of combinational circuits. Concurrency and timing will be discussed in the examples of this chapter. Except for specification of timing parameters, codes discussed in this chapter are synthesizable. A section in this chapter presents rules for writing synthesizable combinational circuits.

Chapter 5 discusses modeling and description of sequential circuits in Verilog. The chapter begins with models of memory and shows how they can be specified in Verilog. Registers, counters, and state machines are discussed in this chapter. A section in this chapter presents rules for writing synthesizable sequential circuits.

Chapter 6 is on writing testbenches in Verilog. The previous two chapters discussed Verilog from a hardware design point of view, and this chapter shows how components described as such can be tested. We talk about data generation, response analysis, and assertion verification.

Chapter 7 covers switch level modeling and detailed representation of signals in Verilog. This material is geared more for those using Verilog as a modeling language and less for designers. VLSI structures can be described by Verilog constructs discussed here.

Chapter 8 shows complete RTL design flow, from problem specification to test. We show several complete examples that take advantage of material of Chapters 4, 5, and 6 for description, simulation, verification, and synthesis of digital systems. Examples in this chapter take advantage of text IO facilities of Verilog for storing test data and circuit responses.

Appendix A contains Verilog keywords. Appendix B lists commonly used system tasks and briefly describes each task. Appendix C lists Verilog compiler directives and explains their use. Appendix D presents the standard IEEE Verilog HDL syntax. Language constructs terminals and nonterminals are presented here in a formal grammar representation. Appendix E presents the OVL assertion monitors. After a brief description of each assertion monitor its parameters and arguments are explained.

#### Suggested Reading Flow

The book teaches the Verilog language for RT level design, simulation, verification, and synthesis of digital systems. For a complete comprehension of these issues, or for a complete one-semester graduate course, the book is recommended in its entirety. However, for specific needs and requirements or for an undergraduate course on automated design methodologies, parts of the book can also be used. The following paragraphs present several such uses.

For a hardware designer interested in learning about synthesis, Chapters 4 and 5 are the most important ones. For such users, Chapter 3 can be used as a reference, and Chapter 6, which is on testbench development, can be studied as needed. When the designer is ready to consider complete systems, Chapter 8 is recommended.

Chapter 2 is introductory and provides an overview of the language. For a student using Verilog in a lower-level undergraduate course, this chapter is a good starting point for learning the language. More complex parts of the language can then be learned as needed.

Chapter 8 can be used for learning computer organization concepts and the use of Verilog in description of these structures. Readers familiar with Verilog can use their knowledge to learn the inter-workings of CPU structures, instruction execution, and testing large systems.

The flow of the book is such that it provides a complete knowledge of Verilog using the same flow as that used in teaching hardware design in most 4-year Computer Engineering programs. The following outlines indicate various applications of the book for beginners, undergraduate students, graduate students, designer engineers, modelers, and system designers.

- 1. General introduction for a lower-level undergraduate course or an entry level design engineer:

- *Chapters 1–2.* Design flow and Verilog overview

- Chapters 4–5. Combinational and sequential circuits for synthesis

- 2. Advanced logic design for a senior-level course or an advanced design engineer with some familiarity with design flow and Verilog syntax:

- Chapters 1-2. A review of Verilog-based design

- Chapter 3. Language semantics and constructs

- *Chapters 4–5.* Combinational and sequential circuits for synthesis

- Chapter 6. Test methods

- 3. Advanced system design for a senior-level course or an advanced system design engineer with some familiarity with design flow and Verilog syntax:

- Chapters 1–2. A review of Verilog-based design

- Chapter 3. Use as reference as needed

- Chapters 4–5. Combinational and sequential circuits for synthesis

- Chapter 6. Test methods

- Chapter 8. Top-down design of systems

- 4. Advanced modeling and system design for a graduate-level course or an advanced VLSI design engineer:

- Chapters 1–2. A review of Verilog-based design

- Chapter 3. Use as reference as needed

- Chapters 4–5. Combinational and sequential circuits for synthesis

- Chapter 6. Test methods

- Chapter 7. Switch level and CMOS modeling

- Chapter 8. Top-down design of systems

- 5. Parallel with undergraduate Computer Engineering program:

- $lue{}$  Use Chapters 1 and 2 early in a digital logic design course

- Use Chapters 4 and 5 in a digital logic design course in parallel with discussion of combinational and sequential circuits

- Use Chapter 6 in a technical elective design course

- Use Chapter 7 in the senior-level VLSI course

- Use Chapter 8 in the Junior or Sophomore computer architecture course

#### **Code Examples**

Among many tasks involved in the preparation of the manuscript, for a book describing a language that is as example oriented as this book, selecting appropriate set of examples and presenting them to the reader are of special importance. For every design example presented in this book, a testbench is generated and the design has been tested. With every example, there is a logic design concept and there are several Verilog constructs and features that are covered. The set of examples is chosen to present the complete Verilog language for synthesis. These examples start with using simple Verilog constructs and progressively move into more complex ones. Parallel with the flow of language constructs, the book starts with using simple logic design concepts, such as using basic gates for combinational circuits, and moves into advanced logic design concepts such as queues and processors.

The CD accompanying this book includes simulation, synthesis, and device programming software tools. Verilog description of the examples of this book and their testbenches are also included on this CD. For the instructors using this book in an educational setting, solutions for the end of chapter problems and Power Point lecture slides can be obtained from the author or the publisher.

#### **Acknowledgments**

Guidelines, comments, reviews, and support of many people helped the development of this book, and the author wishes to thank them. The style used for presenting the material is based on simple examples that cover a certain topic and discussing the issues that the example covers. As with the other books that I have written, I have used guidelines and writing philosophy of the late Professor Fredrick J. Hill of the University of Arizona, with whom I worked many years as a student and a research associate. My students and colleagues were particularly helpful in the development of this book. In the past 15 years, my students at the University of Tehran, Northeastern University and National Technological University have been very helpful in bringing up ideas for more illustrative examples. Many examples come from exam and homework questions that these students had to struggle with.

At the start of this writing project, my associate, Ms. Fatemeh Asgari assumed responsibility for managing the preparation of the manuscript. Organizing the efforts for manuscript preparation, managing the timing

#### xvi Preface

of this task with my many other tasks has been a very challenging task for her. Her crystal ball always told the truth about how bad I would miss my deadlines. Students at the University of Tehran, Armin Alaghi, Najmeh Fakhraie, Amirali Ghofrani, Aida Hasani, and Mahsan Rofouei, were very helpful in completion of this project. They helped reviewing the manuscript, coding, preparing the artwork, and suggesting ways of improving the flow of the book for different levels of audiences.

Most of all, I thank my wife, Irma Navabi, for help encouragement and understanding of my working habits. Such an intensive work could not be done if I did not have support of my wife and my two sons, Aarash and Arvand. I thank them for this and other scientific achievements I have had.

Zainalabedin Navabi, Ph.D.

Boston, Massachusetts

navabi@ece.neu.edu

Chapter

1

## Digital System Design Automation with Verilog

As the size and complexity of digital systems increase, more computer-aided design (CAD) tools are introduced into the hardware design process. Early simulation and primitive hardware generation tools have given way to sophisticated design entry, verification, high-level synthesis, formal verification, and automatic hardware generation and device programming tools. Growth of design automation tools is largely due to hardware description languages (HDLs) and design methodologies that are based on these languages. Based on HDLs, new digital system CAD tools have been developed and are now widely used by hardware designers. At the same time research for finding better and more abstract hardware languages continues. One of the most widely used HDLs is the Verilog HDL. Because of its wide acceptance in digital design industry, Verilog has become a must-know for design engineers and students in computer-hardware-related fields.

This chapter presents tools and environments that are based on Verilog and are available to a hardware designer for automating his or her design process, and hence improving the final product's time to market. We discuss steps involved in taking a hierarchical, high-level design from a Verilog description of the design to its implementation in hardware. Processes and terminologies are illustrated here. We discuss available electronic design automation (EDA) tools that are based on Verilog, and talk about their role in an automated design environment. The last section of this chapter discusses some of the properties of Verilog that make this language a good choice for designers and modelers of hardware.

1

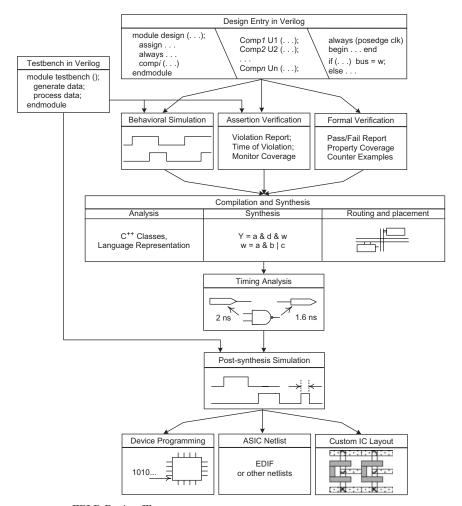

#### 1.1 Digital Design Flow

For the design of a digital system using an automated design environment, the design flow begins with specification of the design at various levels of abstraction and ends with generating netlist for an application specific integrated circuits (ASIC), layout for a custom IC, or a program for a programmable logic devices (PLD). Figure 1.1 shows steps involved in this design flow.

In the design entry phase, a design is specified as a mixture of behavioral Verilog code, instantiation of Verilog modules, and bus and wire assignments. A design engineer is also responsible for generating testbenches

Figure 1.1 FPLD Design Flow

for his or her design for verification of the design and later for verifying the synthesis output. Design verification can be done by simulation, assertion verification, formal verification, or a mix of all three. After performing this design validation phase (this is called the presynthesis verification), this design is taken through the synthesis process to translate it into actual hardware of a target device. Here, target device refers to the specific field programmable logic device (FPLD) that is being programmed, the ASIC that is being manufactured by an outside source, or the custom IC that is being fabricated. After the synthesis process and before the actual hardware is generated, another simulation, which is referred to as postsynthesis simulation, is done. This simulation can take advantage of the same testbench generated for the Verilog model of the system before it is synthesized. This way, the behavioral model of the design and its hardware model are tested with the same data. The difference between pre- and postsynthesis simulations is in the level of details obtained from each simulation.

The sections that follow elaborate on each of the blocks shown in Fig. 1.1. Most Verilog based EDA environments provide blocks shown in this figure.

#### 1.1.1 Design entry

The first step in the design of a digital system is the design entry phase. In this phase, the design is described in Verilog in a top-down hierarchical fashion. A complete design may consist of components at the gate or transistor level, behavioral parts describing high-level functionality of a hardware module, or components described by their bussing structure.

Because high-level Verilog designs are usually described at the level that specifies system registers and transfer of data between registers through busses, this level of system description is referred to as register transfer level (RTL). A complete design described as such has a clear hardware correspondence. Verilog constructs used in an RT level design are procedural statements, continuous assignments, and instantiation statements.

Verilog *procedural statements* are used for high-level behavioral descriptions. A system or a component is described in a procedural fashion similar to the way processes are described in a software language. For example, we can describe a component by checking its input conditions, setting flags, waiting for events to occur, monitoring handshaking signals, and issuing outputs. Describing a system procedurally, Verilog **if-else**, **case** and other software-language-like constructs can be used.

Verilog *continuous assignments* are statements for representing logic blocks, bus assignments, and bus and input/output interconnect specifications. Combined with boolean and conditional operations, these language constructs can be used for describing components and systems in terms of their register and bus assignments.

#### 4 Chapter One

Verilog *instantiation statements* are for using lower-level components in an upper-level design. Instead of describing behavior, functionality, or bussing of a system, we can describe a system in Verilog in terms of its lower-level components. These subcomponents can be as small as a gate or a transistor, or as large as a complete processor.

#### 1.1.2 Testbench in Verilog

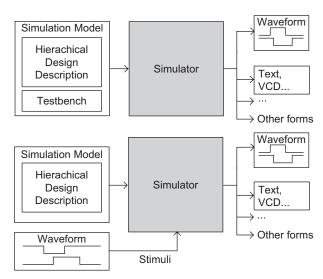

A system designed in Verilog must be simulated and tested for functionality before it is turned into hardware. In this simulation pass, design errors and incompatibility of components used in the design can be detected. Simulating a design requires generation of test data and observation of simulation results. This process can be done by use of a Verilog module that is referred to as a testbench. A Verilog testbench uses high-level constructs of this language for data generation, response monitoring, and even handshaking with the design. Inside the testbench, the design that is being simulated is instantiated. The testbench together with the design forms a simulation model used by a Verilog simulation engine.

#### 1.1.3 Design validation

An important task in any digital design is design validation. Design validation is the process that a designer checks his or her design for any design flaws that may have occurred in the design process. A design flaw can happen due to ambiguous problem specifications, designer errors, or incorrect use of parts in the design. Design validation can be done by simulation, assertion verification, or formal verification.

**1.1.3.1 Simulation.** Simulation for design validation is done before a design is synthesized. This simulation pass is also referred to as behavioral, RT level, or presynthesis simulation. At the RT level a design includes clock-level timing but no gate and wire delays are included. Simulation at this level is accurate to the clock level. Timing of RT-level simulation is at the clock level and does not usually consider hazards, glitches, race conditions, setup and hold violations, and other detailed timing issues. The advantage of this simulation is its speed compared with simulations at the gate or transistor levels.

Simulation of a design requires test data, and usually Verilog simulation environments provide various methods for application of these data to the design being tested. Test data can be generated graphically using waveform editors, or through a testbench. Figure 1.2 shows two alternatives for defining test input data for a simulation engine. Outputs of simulators are in the form of waveforms (for visual inspection) and text for large designs for machine processing.

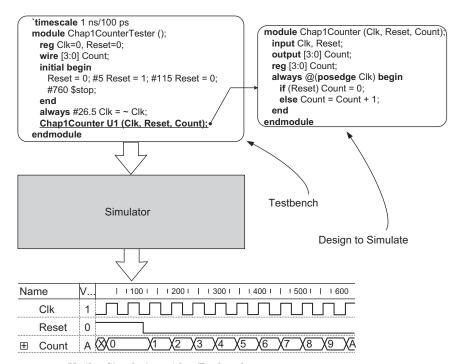

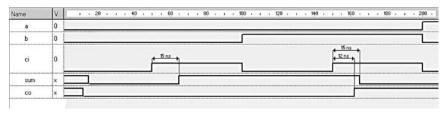

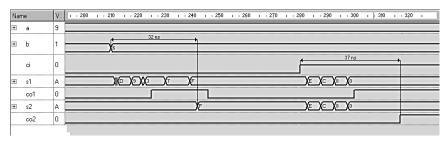

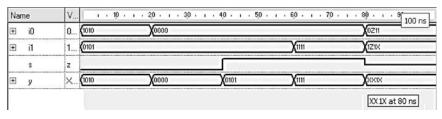

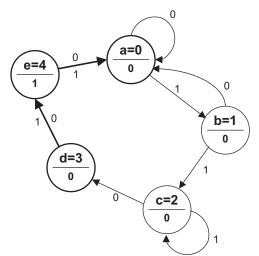

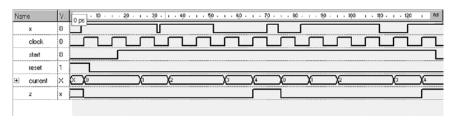

Figure 1.2 Using a Testbench or a Waveform Editor for Simulation

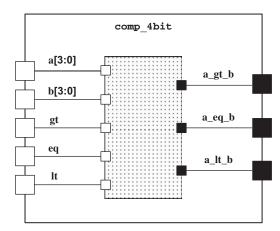

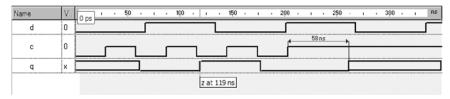

For simulating with a Verilog testbench, the testbench instantiates the design under test, and as part of the code of the testbench it applies test data to the instantiated circuit. Figure 1.3 shows a Verilog code of a counter circuit, its testbench, and its simulation results in form of a waveform. As shown here, simulation validates the functionality of the counter circuit being tested. With every clock pulse the counter is incremented by 1. Note in the timing diagram that the counter output changes with the rising edge of the clock and no gate delays and propagation delays are shown. Simulation results show the correct functionality of the counter regardless of the clock frequency.

Obviously, an actual hardware component behaves differently. Based on the timing and delays of the parts used, there will be a nonzero delay between the active edge of the clock and the counter output. Furthermore, if the clock frequency applied to an actual part is too fast for propagation of values within the gates and transistors of a design, the output of the design becomes unpredictable.

The simulation shown here is not provided with the details of the timing of the hardware being simulated. Therefore, potential timing problems of the hardware that are due to gate delays cannot be detected. This is typical of a presynthesis or high-level behavioral simulation. What is being verified in Fig. 1.3 is that our counter counts binary numbers. How fast the circuit works and what clock frequency it requires can only be verified after the design is synthesized.

Figure 1.3 Verilog Simulation with a Testbench

- 1.1.3.2 Assertion verification. Instead of having to inspect simulation results manually or by developing sophisticated testbenches, assertion monitors can be used to continuously check for design properties while the design is being simulated. Assertion monitors are put in the design being simulated by the designer. The designer decides that if the design functions correctly, certain conditions have to be met. These conditions are regarded as design properties, and assertion monitors are developed by designer to assert that these properties are not violated. An assertion monitor fires if a design property put in by the designer is violated. This alerts the designer that the design is not functioning according to the designer's expectation. Open verification library (OVL) provides a set of assertion monitors for monitoring common design properties. Designers can use their own assertions and use them in conjunction with their testbenches.

- **1.1.3.3 Formal verification.** Formal verification is the process of checking a design against certain properties. When a design is completed, the designer develops a set of properties reflecting correct behavior of his or her design. A formal verification tool examines the design to make sure that the described properties hold under all conditions. If a situation

is found that the property will not hold, the property is said to have been violated. Input conditions that make a property fail are regarded as the property's counter examples. Property coverage indicates how much of the complete design is exercised by the property.

#### 1.1.4 Compilation and synthesis

Synthesis is the process of automatic hardware generation from a design description that has an unambiguous hardware correspondence. A Verilog description for synthesis cannot include signal and gate level timing specifications, file handling, and other language constructs that do not translate to sequential or combinational logic equations. Furthermore, Verilog descriptions for synthesis must follow certain styles of coding for combinational and sequential circuits. These styles and their corresponding Verilog constructs are defined under Verilog for RTL synthesis.

In the design process, after a design is successfully entered and its presynthesis simulation results have been verified by the designer, it must be compiled to make it one step closer to an actual hardware on silicon. This design phase requires specification of the hardware that the design is to be realized in. For example, we have to specify a specific ASIC, or a field programmable gate array (FPGA) part as our "target hardware." When the target hardware is specified, technology files of that hardware (ASIC, FPGA, or custom IC) with detailed timing and functional specification become available to the compilation process. The compilation process, translates various parts of the design to an intermediate format (analysis phase), links all parts together, generates the corresponding logic (synthesis phase), places and routes components of the target hardware, and generates timing details.

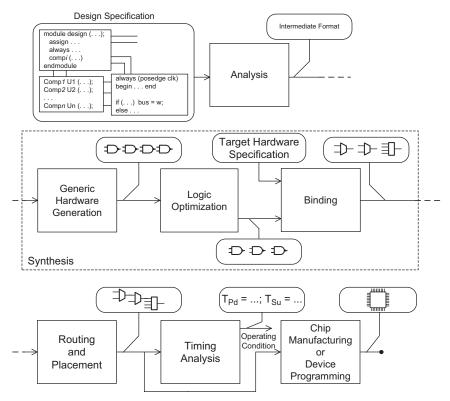

Figure 1.4 shows the compilation process and a graphical representation for each of the compilation phase outputs. As shown, the input of this phase is a hardware description that consists of various levels of Verilog, and its output is a detailed hardware for programming an FPLDor manufacturing an ASIC.

- **1.1.4.1 Analysis.** A complete design that is described in Verilog may consist of behavioral Verilog, bus and interconnection specifications, and wiring of other Verilog components. Before the complete design is turned into hardware, the design must be analyzed and a uniform format must be generated for all parts of the design. This phase also checks the syntax and semantics of the input Verilog code.

- **1.1.4.2 Generic hardware generation.** After obtaining a uniform presentation for all components of a design, the synthesis pass begins its

#### 8 Chapter One

Figure 1.4 Compilation and Synthesis Process

operation by turning the design into a generic hardware format, such as a set of boolean expressions or a netlist of basic gates.

**1.1.4.3 Logic optimization.** The next phase of synthesis, after a design has been converted to a set of boolean expressions, is the logic optimization phase. This phase is responsible for reducing expressions with constant input, removing redundant logic expressions, two-level minimization, and multilevel minimization that include logic sharing.

This is a very computationally intensive process, and some tools allow users to decide on the level of optimization. Output of this phase is in the form of boolean expressions, tabular logic representations, or primitive gate netlists.

**1.1.4.4 Binding.** After logic optimization, the synthesis process uses information from target hardware to decide exactly what logic elements and cells are needed for the realization of the circuit that is being

designed. This process is called binding and its output is specific to the FPLD, ASIC, or custom IC being used.

**1.1.4.5** Routing and placement. The routing and placement phase decides on the placement of cells of the target hardware. Wiring inputs and outputs of these cells through wiring channels and switching areas of the target hardware are determined by the routing and placement phase. The output of this phase is specific to the hardware being used and can be used for programming an FPLD or manufacturing an ASIC.

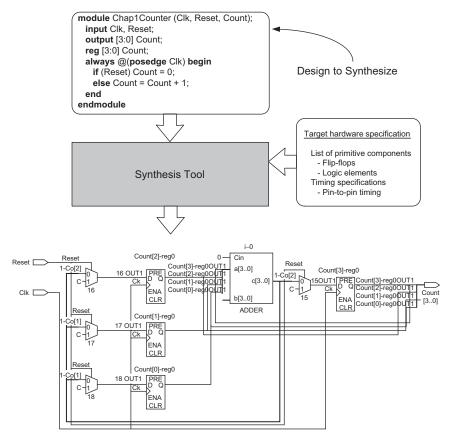

An example of a synthesis run is shown in Fig. 1.5. In this figure, the counter circuit used in the simulation run of Fig. 1.3 is being synthesized. In addition to the Verilog description of the design, the synthesis tool shown requires specification of the target hardware to synthesize to. The output of the synthesis tool is a list of gates and flip-flops available

Figure 1.5 An Example Synthesis Run

#### 10 Chapter One

in the target hardware, and their interconnections. A graphical representation of this output that is automatically generated by the synthesis tool of Altera's Quartus II is shown in Fig. 1.5.

#### 1.1.5 Postsynthesis simulation

After synthesis is done, the synthesis tool generates a complete netlist of target hardware components and their timings. The details of gates used for the implementation of the design are described in this netlist. The netlist also includes wiring delays and load effects on gates used in the postsynthesis design. The netlist output is made available in various netlist formats including Verilog. Such a description can be simulated and its simulation is referred to postsynthesis simulation. Timing issues, determination of a proper clock frequency and race, and hazard considerations can only be checked by a postsynthesis simulation run after a design is synthesized. As shown in Fig. 1.1, the same testbench testing the original Verilog design before synthesis can be used for postsynthesis simulation.

Due to delays of wires and gates, it is possible that the behavior of a design as intended by the designer and its behavior after postsynthesis simulation are different. In this case, the designer must modify his or her design and try to avoid close timings and race situations.

#### 1.1.6 Timing analysis

As shown in Fig. 1.1, as part of the compilation process, or in some tools after the compilation process, there is a timing analysis phase. This phase generates worst-case delays, clocking speed, delays from one gate to another, as well as required setup and hold times. Results of timing analysis appear in tables and/or graphs. Designers use this information to decide on their clocking speed and, in general, speed of their circuits.

#### 1.1.7 Hardware generation

The last stage in an automated Verilog-based design is hardware generation. This stage generates a netlist for ASIC manufacturing, a program for programming FPLDs, or layout of custom IC cells.

#### 1.2 Verilog HDL

The previous section showed steps involved in taking an RT level design from a Verilog description to hardware implementation. This design process is only possible because Verilog is a language that can be understood by system designers, RT level designers, test engineers, simulators, synthesis tools, and machines. Because of this important role in design,

Verilog has become an IEEE standard. The standard is used by users as well as tool developers.

#### 1.2.1 Verilog evolution

Verilog was designed in early 1984 by Gateway Design Automation. Initially the original language was used as a simulation and verification tool. After the initial acceptance of this language by electronic industry, a fault simulator, a timing analyzer, and later in 1987, a synthesis tool was developed based on this language. Gateway Design Automation and its Verilog-based tools were later acquired by Cadence Design System. Since then, Cadence has been a strong force behind popularizing the Verilog hardware description language.

In 1987 VHDL became an IEEE standard hardware description language. Because of its Department of Defense (DoD) support, VHDL was adapted by the U.S. government for related projects and contracts. In an effort for popularizing Verilog, in 1990, OVI (Open Verilog International) was formed and Verilog was placed in public domain. This created a new line of interest in Verilog for the users and EDA vendors.

In 1993, efforts for standardization of this language started. Verilog became the IEEE standard, IEEE Std. 1364-1995, in 1995. Already having simulation tools, synthesizers, fault simulation programs, timing analyzers, and many of their design tools developed for Verilog, this standardization helped further acceptance of Verilog in electronic design communities.

A new version of Verilog was approved by IEEE in 2001. This version that is referred to as Verilog-2001 is the present standard used by most users and tool developers. New features for external file access for read and write, library management, constructs for design configuration, higher abstraction level constructs, and constructs for specification of iterative structures, are some of the features added to this version of Verilog. Work on improving this standard continues in various IEEE sponsored study groups.

#### 1.2.2 Verilog attributes

Verilog is a hardware description language for describing hardware from transistor level to behavioral. The language supports timing constructs for switch level timing simulation and at the same time, it has features for describing hardware at the abstract algorithmic level. A Verilog description may consist of a mix of modules at various abstraction levels with different degrees of detail.

**1.2.2.1 Switch level.** Features of the language that make it ideal for switch level modeling and simulation includes primitive unidirectional

and bidirectional switches with parameters for delay and charge storage. Circuit delays may be modeled as propagation delay, rise and fall delay, and line delays. The charge storage feature at this level of abstraction in Verilog makes this language capable of describing dynamic complimentary metal oxide semicondutor (CMOS) and metal oxide semiconductor (MOS) circuits.

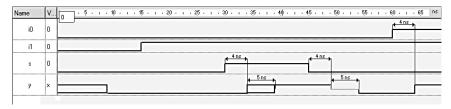

- **1.2.2.2 Gate level.** Gate level primitives with predefined parameters provide a convenient platform for netlist representation and gate level simulation. For more detailed and special purpose gate simulations, gate components may be defined at the behavioral level. Verilog also provides utilities for defining primitives with special functionalities. A simple 4-value logic system is used in Verilog for signal values. However, for more accurate logic modeling, Verilog signals also include 16 levels of strength in addition to the four values.

- **1.2.2.3** Pin-to-pin delay. A utility for timing specification of components at the input/output level is provided in Verilog. This utility can be used for back annotation of timing information in original predesigned descriptions. Moreover, the pin-to-pin language facility enables modelers to finetune timing behavior of their models based on physical implementations.

- **1.2.2.4 Bussing specifications.** Bus and register modeling utilities are provided in Verilog. For various bus structures, Verilog supports predefined wire and bus resolution functions using its 4-value logic value system. Combination of bus logic and resolution-functions enable modeling of most physical bus types. For register modeling, high-level clock representation and timing-control constructs can be used for representation of registers with various clocking and resetting schemes.

- **1.2.2.5 Behavioral level.** Procedural blocks of Verilog enable algorithmic representations of hardware structures. Constructs similar to those in software programming languages are provided for describing hardware at this level.

- 1.2.2.6 System utilities. System tasks in Verilog provide designers with tools for testbench generation, file access for read and write, data handling, data generation, and special hardware modeling. System utilities for reading memory and programmable logic array (PLA) images provide convenient ways of modeling these components. Verilog display and I/O tasks can be used to handle all inputs and outputs for data application and simulation. Verilog allows random access to files for read and write operations.

**1.2.2.7 PLI.** Programming language interface (PLI) of Verilog provides an environment for accessing Verilog data structures using a library of C-language functions.

#### 1.2.3 The Verilog language

The Verilog HDL satisfies all requirements for design and synthesis of digital systems. The language supports hierarchical description of hardware from system to gate or even switch level. Verilog has strong support at all levels for timing specification and violation detection. Timing and concurrency required for hardware modeling are specially emphasized.

In Verilog a hardware component is described by the *module\_declaration* language construct. Description of a module specifies a component's input and output list as well as internal component busses and registers. Within a **module**, concurrent assignments, component instantiations, and procedural blocks can be used to describe a hardware component.

Several modules can hierarchically be instantiated to form other hardware structures. Leaves of a hierarchical design specification may be modules, primitives, or user defined primitives. For simulating a design, it is expected that all leaves of the hierarchy are individually compiled.

Many Verilog tools and environments exist that provide simulation, fault simulation, formal verification, and synthesis. Simulation environments provide graphical front-end programs and waveform editing and display tools. Synthesis tools are based on a subset of Verilog. For synthesizing a design, target hardware, e.g., specific FPGA or ASIC, must be known.

#### 1.3 Summary

This chapter gave an overview of mechanisms, tools, and processes used for taking a design from the design stage to a hardware implementation. This overview contained information that will become clearer in the chapters that follow. This chapter also provided the reader with the history of Verilog evolution. With this standard HDL, the efforts of tool developers, researchers, and software vendors have become more focused, resulting in better tools and more uniform environments. The next chapter presents an overview of Verilog.

#### **Problems**

**1.1** Study Altera's FPGA design environment and see their simulation and synthesis environments. How do you compare Altera's environment with the simulation and synthesis environments discussed in this chapter?

#### 14 Chapter One

- **1.2** Search for several commercial formal verification tools and generate a report of their input formats, capabilities, and their verification utilities.

- **1.3** Study Accellera's OVL library and discuss how this library helps the design automation process.

- **1.4** Study SystemC and discuss tools available for this language.

- **1.5** Study the VHDL hardware description language and discuss tools available for this language.

#### Suggested Reading

- Accellera, Open Verification Library: Assertion Monitor Reference Manual, www.accellera.org, v1.0, 2005.

- Bening, L., and H. D. Foster, *Principles of Verifiable RTL Design Second Edition–A Functional Coding Style Supporting Verification Processes in Verilog*, 2d ed. Springer, Boston, MA, 2001, ISBN: 0792373685.

- Brown, S., and Z. Vranesic, Fundamentals of Digital Logic with Verilog Design, McGraw-Hill, New York, 2002, ISBN: 0-07-283878-7.

- IEEE Std 1364-2001, IEEE Standard Verilog Language Reference Manual, SH94921-TBR (print) SS94921-TBR (electronic), ISBN 0-7381-2827-9 (print and electronic), 2001.

- IEEE Std 1076-2002, IEEE Standard VHDL Language Reference Manual, SH94983-TBR (print) SS94983-TBR (electronic), ISBN 0-7381-3247-0 (print) 0-7381-3248-9 (electronic), 2002.

- Lam, W. K., Hardware Design Verification: Simulation and Formal Method-Based Approaches, Prentice Hall PTR, New Jersey, 2005, ISBN: 0131433474.

- Navabi, Z., Digital Design and Implementation with Field Programmable Devices, Kluwer Academic Publishers, Boston, MA, 2005, ISBN: 1-4020-8011-5.

- Navabi, Z., Verilog Computer-Based Training Course, CBT CD with hardcopy User's manual, McGraw-Hill, New York, 2002, ISBN 0-07-137473-6.

Chapter

2

## Register Transfer Level Design with Verilog

The intent of this chapter is to present an overview of Verilog and the design styles in which this language is used. Various concepts of a language, be it a software or a hardware language, are interdependent. A general knowledge of the language is therefore needed before more detailed features of the language can be discussed. This chapter discusses register transfer level (RTL) design of digital systems and shows how Verilog is used for description, testing, simulation, and synthesis of various RT level components of a design. With this presentation, we will also give an overview of Verilog and set the stage ready for more elaborate discussion of Verilog constructs in the chapters that follow.

In the sections that follow we will first discuss RT level design and how a complete system is put together at this abstraction level. The section that follows this introductory material presents basic structures of Verilog such as modules, ports, and utilities for test and verification of design components. The rest of this chapter discusses coding of a complete RT level design in Verilog. This part serves as an overview of the complete Verilog HDL language.

#### 2.1 RT Level Design

Design of small hardware components can usually be done by describing the hardware for synthesis and synthesizing and implementing the design by appropriate computer aided design tools. On the other hand, a large design requires proper planning, architectural design, and partitioning before its various parts can be written in Verilog for synthesis. Taking a high-level description of a design, partitioning it, coming up with

#### 16 Chapter Two

an architecture for it (i.e., designing its bussing structure), and then describing and implementing various components of this architecture is referred to as RT level design.

#### 2.1.1 Control/data partitioning

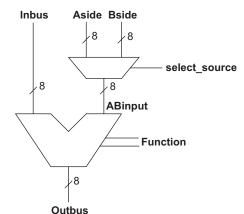

The first step in an RT level design is the partitioning of the design into a data part and a control part. The data part consists of data components and the bussing structure of the design and the control part is usually a state machine generating control signals that control the flow of data in the data part.

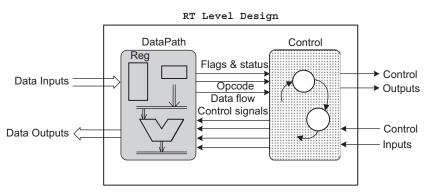

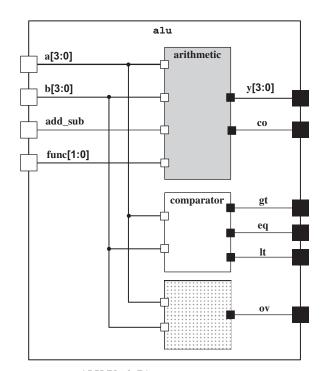

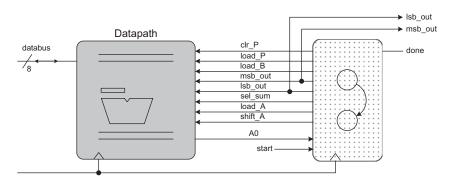

Figure 2.1 shows a general sketch of an RT level design that is partitioned into its data and control parts. We will use this diagram to discuss the two partitions and at the same time show how Verilog may be used for describing an RTL circuit.

#### 2.1.2 Data part

The data part of an RTL design consists of the interconnection of data components that are, registers, combinational logic units, register files, and busses that interconnect them. The data part, which we also refer to as the data path, has external data inputs and outputs, as well as control inputs and outputs from and to the control part. Figure 2.2 shows partial code of the data part of Fig. 2.1 described in Verilog. This partial code shows ports of the *DataPath* **module** and indicates that within this module various data components are specified. Control signals are inputs to the data part and are sent to the data components and busses. This code shows the module header including its name and its ports. Following the header, inputs and outputs, and their dimensions are declared. Texts that are followed by // are comments.

A data component has certain control signals that control its clocking and/or its functionalities.

Figure 2.1 Control/Data Partitioning

```

module DataPath

(DataInput, DataOutput, Flags, Opcodes, ControlSignals);

input [15:0] DataInputs;

output [15:0] DataOutputs;

output Flags, ...;

output Opcodes, ...;

input ControlSignals, ...;

// instantiation of data components

// ...

// interconnection of data components

// bussing specification

endmodule

```

Figure 2.2 DataPath Module

A module describing a typical data component shows how the component uses its input control signals to perform various operations on its data inputs. Figure 2.3 shows a partial code of a data component.

Busses in the data part of an RTL design have control signals that select their sources and routing of data from one data component to another. The data part has output signals going to the control part that provide flags and status of the data.

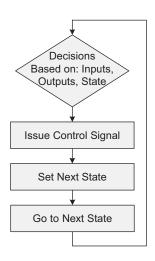

#### 2.1.3 Control part

The control part of an RTL design takes control inputs from the data part and external control inputs and depending on its state makes decisions as to when and what control signals to issue.

The control part, which we also refer to as the control unit, consists of one or more state machines that keep the state of the circuit, make decisions based on the current data and data status, and control how data is routed and what operations are performed on the data in the data part.

```

module DataComponent (DataIn, DataOut, ControlSignals);

input [7:0] DataIn;

output [7:0] DataOut;

input ControlSignals;

// Depending on ControlSignals

// Operate on DataIn and

// Produce DataOut

endmodule

```

Figure 2.3 Partial Verilog Code of a Data Component

Figure 2.4 Outline of a Controller

Partial Verilog module of Fig. 2.4 shows an outline of tasks handled by the control unit of an RTL design.

#### 2.2 Elements of Verilog

Constructs of the Verilog language are designed for describing hardware modules and primitives. This section presents basic constructs of the language for describing a hardware module.

#### 2.2.1 Hardware modules

The Verilog hardware description language (HDL) is used to describe hardware modules of a system and complete systems. Therefore, the main component of the language, which is a *module*, is dedicated for this purpose. As shown in Fig. 2.5, a module description consists of the keyword **module**, the name of the module, a list of ports of the hardware module, the module functionality specification, and the keyword **end-module**. Following a module name and its list of ports, usually variables, wires, and module parameters are declared. After the declarations, statements in a module specify its functionality. This part defines how output ports react to changes on the input ports.

```

module module-name

List of ports;

Declarations

...

Functional specification of module

...

endmodule

```

Figure 2.5 Module Specifications

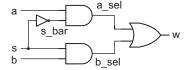

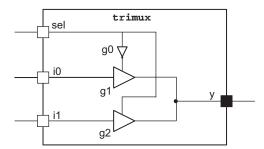

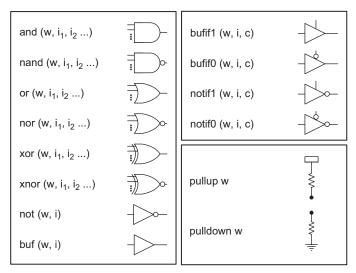

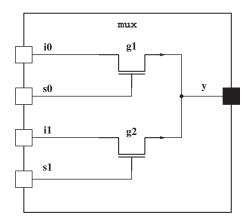

Figure 2.6 A Multiplexer Using Basic Gates

As in software languages, there is usually more than one way a module can be described in Verilog. Various descriptions of a component may correspond to descriptions at various levels of abstraction or to various levels of detail of the functionality of a module. One module description may be at the behavioral level of abstraction with no timing details, while another description for the same component may include transistor-level timing details. A module may be part of a library of predesigned library components and include detailed timing and loading information, while a different description of the same module may be at the behavioral level for input to a synthesis tool. It must be noted that descriptions of the same module need not behave in exactly the same way nor is it required that all descriptions describe a behavior correctly. In a fault simulation environment, faulty modules may be developed to study various failure forms of a component.

In the sections that follow we show a small example and several alternative ways it can be described in Verilog. This presentation is to serve as an introduction to various forms of Verilog constructs for the description of hardware.

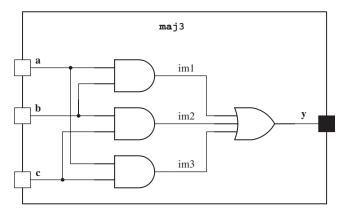

# 2.2.2 Primitive instantiations

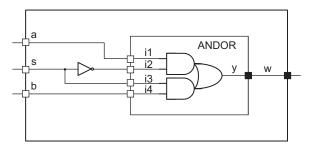

Verilog uses different constructs for describing a module with different levels of detail. Verilog basic logic gates are called primitives and for describing a component using these primitives, a construct called primitive instantiation is used. See for example the multiplexer of Fig. 2.6 that is made of AND and OR gates. This structure can be described in Verilog as shown in Fig. 2.7.

```

module MultiplexerA (input a, b, s, output w);

wire a_sel, b_sel, s_bar;

not U1 (s_bar, s);

and U2 (a_sel, a, s_bar);

and U3 (b_sel, b, s);

or U4 (w, a_sel, b_sel);

endmodule

```

Figure 2.7 Primitive Instantiations

```

module MultiplexerB (input a, b, s, output w);

assign w = (a & ~s) | (b & s);

endmodule

```

Figure 2.8 Assign Statement and Boolean

The first line of this code contains the name of the module, *MultiplexerA*, and its input and output ports. Following this line, intermediate wires are declared. The rest of this code consists of instantiation of **not**, **and**, and **or** gates. These instantiations are done according to the diagram of Fig. 2.6, and their wirings are as indicated in this diagram.

# 2.2.3 Assign statements

Instead of describing a component using primitive gates, boolean expressions can be used to describe the logic, and Verilog **assign** statements can be used for assigning results of these expressions to various outputs. Our simple multiplexer example can be described as shown in Fig. 2.8.

The statement shown in the body of the MultiplexerB module continuously drives w with its right-hand side expression.

# 2.2.4 Conditional expression

In cases where the operation of a unit is too complex to be described by boolean expressions, conditional expressions can be used. Our multiplexer example is described in Fig. 2.9 using an **assign** statement and a conditional operation.

Because conditional expressions mimic if-then-else behavior of software languages, they are very effective in describing complex functionalities. Furthermore, the nesting capability of the conditional operator makes it useful in describing a behavior in a very compact way.

### 2.2.5 Procedural blocks

In cases where the operation of a unit is too complex to be described by assignment of boolean or conditional expressions, higher-level procedural

```

module MultiplexerC (input a, b, s, output w);

assign w = s ? b : a;

endmodule

```

Figure 2.9 Assign Statement and Condition Operator

```

module MultiplexerD (input a, b, s, output w);

reg w;

always @ (a, b, s) begin

if (s) w = b;

else w = a;

end

endmodule

```

Figure 2.10 Procedural Statement

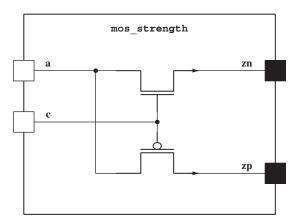

constructs should be used. Verilog's main construct for procedural specification of hardware is the **always** statement used in the example of Fig. 2.10.